IMS: ccNOos, Declarations for straight C and C++ More...

Go to the source code of this file.

Detailed Description

IMS: ccNOos, Declarations for straight C and C++

Copyright 2021 InMechaSol, Inc

Licensed under the Apache License, Version 2.0(the "License"); you may not use this file except in compliance with the License. You may obtain a copy of the License at

http://www.apache.org/licenses/LICENSE-2.0

Unless required by applicable law or agreed to in writing, software distributed under the License is distributed on an "AS IS" BASIS, WITHOUT WARRANTIES OR CONDITIONS OF ANY KIND, either express or implied. See the License for the specific language governing permissions and limitations under the License.

Notes: (.c includes .h) - for straight C or (.cpp includes .c which includes .h) - for C++ wrapped straight C Always compiled to a single compilation unit, either C or CPP, not both

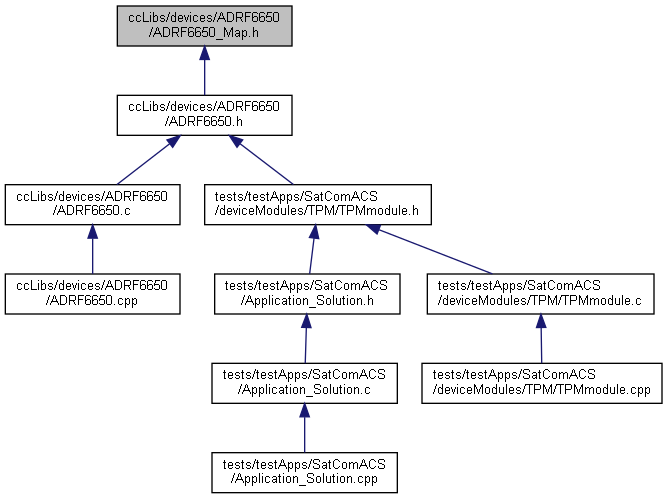

Definition in file ADRF6650_Map.h.

Macro Definition Documentation

◆ MASK_ARSTB_BLOCK_AUTOCAL

| #define MASK_ARSTB_BLOCK_AUTOCAL 0b00100000 |

Definition at line 302 of file ADRF6650_Map.h.

◆ MASK_ARSTB_BLOCK_DSMALL

| #define MASK_ARSTB_BLOCK_DSMALL 0b00000001 |

Definition at line 307 of file ADRF6650_Map.h.

◆ MASK_ARSTB_BLOCK_DSMCORE

| #define MASK_ARSTB_BLOCK_DSMCORE 0b00000010 |

Definition at line 306 of file ADRF6650_Map.h.

◆ MASK_ARSTB_BLOCK_DSMOSTG

| #define MASK_ARSTB_BLOCK_DSMOSTG 0b00000100 |

Definition at line 305 of file ADRF6650_Map.h.

◆ MASK_ARSTB_BLOCK_LKD

| #define MASK_ARSTB_BLOCK_LKD 0b01000000 |

Definition at line 301 of file ADRF6650_Map.h.

◆ MASK_ARSTB_BLOCK_NDIV

| #define MASK_ARSTB_BLOCK_NDIV 0b00010000 |

Definition at line 303 of file ADRF6650_Map.h.

◆ MASK_ARSTB_BLOCK_RDIV

| #define MASK_ARSTB_BLOCK_RDIV 0b00001000 |

Definition at line 304 of file ADRF6650_Map.h.

◆ MASK_ATTEN_READBACK_CH1

| #define MASK_ATTEN_READBACK_CH1 0b11111111 |

Definition at line 174 of file ADRF6650_Map.h.

◆ MASK_ATTEN_READBACK_CH2

| #define MASK_ATTEN_READBACK_CH2 0b11111111 |

Definition at line 177 of file ADRF6650_Map.h.

◆ MASK_BICP

| #define MASK_BICP 0b11111111 |

Definition at line 405 of file ADRF6650_Map.h.

◆ MASK_BLEED_EN

| #define MASK_BLEED_EN 0b00000001 |

Definition at line 396 of file ADRF6650_Map.h.

◆ MASK_BLEED_POL

| #define MASK_BLEED_POL 0b01000000 |

Definition at line 394 of file ADRF6650_Map.h.

◆ MASK_BYPASS_TDD

| #define MASK_BYPASS_TDD 0b00000001 |

Definition at line 193 of file ADRF6650_Map.h.

◆ MASK_CHIPTYPE

| #define MASK_CHIPTYPE 0b11111111 |

Definition at line 148 of file ADRF6650_Map.h.

◆ MASK_CP_CURRENT

| #define MASK_CP_CURRENT 0b00001111 |

Definition at line 402 of file ADRF6650_Map.h.

◆ MASK_CP_HIZ

| #define MASK_CP_HIZ 0b00000011 |

Definition at line 390 of file ADRF6650_Map.h.

◆ MASK_CSB_STALL

| #define MASK_CSB_STALL 0b01000000 |

Definition at line 133 of file ADRF6650_Map.h.

◆ MASK_DISABLE_CAL

| #define MASK_DISABLE_CAL 0b01000000 |

Definition at line 380 of file ADRF6650_Map.h.

◆ MASK_DISABLE_DBLBUFFERING

| #define MASK_DISABLE_DBLBUFFERING 0b00000010 |

Definition at line 482 of file ADRF6650_Map.h.

◆ MASK_DISABLE_FREQHOP

| #define MASK_DISABLE_FREQHOP 0b00000100 |

Definition at line 481 of file ADRF6650_Map.h.

◆ MASK_DISABLE_PHASEADJ

| #define MASK_DISABLE_PHASEADJ 0b00000001 |

Definition at line 483 of file ADRF6650_Map.h.

◆ MASK_DOUBLER_EN

| #define MASK_DOUBLER_EN 0b00001000 |

Definition at line 367 of file ADRF6650_Map.h.

◆ MASK_DSM_LAUNCH_DLY

| #define MASK_DSM_LAUNCH_DLY 0b00011000 |

Definition at line 480 of file ADRF6650_Map.h.

◆ MASK_DVGA_5V_SEL

| #define MASK_DVGA_5V_SEL 0b10000000 |

Definition at line 227 of file ADRF6650_Map.h.

◆ MASK_DVGA_CH1_RSTB

| #define MASK_DVGA_CH1_RSTB 0b00000001 |

Definition at line 170 of file ADRF6650_Map.h.

◆ MASK_DVGA_CH2_RSTB

| #define MASK_DVGA_CH2_RSTB 0b00000010 |

Definition at line 169 of file ADRF6650_Map.h.

◆ MASK_DVGA_ENB_CH1

| #define MASK_DVGA_ENB_CH1 0b01000000 |

Definition at line 187 of file ADRF6650_Map.h.

◆ MASK_DVGA_ENB_CH1_MASK

| #define MASK_DVGA_ENB_CH1_MASK 0b00100000 |

Definition at line 212 of file ADRF6650_Map.h.

◆ MASK_DVGA_ENB_CH2

| #define MASK_DVGA_ENB_CH2 0b10000000 |

Definition at line 186 of file ADRF6650_Map.h.

◆ MASK_DVGA_ENB_CH2_MASK

| #define MASK_DVGA_ENB_CH2_MASK 0b01000000 |

Definition at line 211 of file ADRF6650_Map.h.

◆ MASK_DVGA_FA_STEP

| #define MASK_DVGA_FA_STEP 0b01100000 |

Definition at line 228 of file ADRF6650_Map.h.

◆ MASK_DVGA_GAIN_CH1

| #define MASK_DVGA_GAIN_CH1 0b00111111 |

Definition at line 237 of file ADRF6650_Map.h.

◆ MASK_DVGA_GAIN_CH2

| #define MASK_DVGA_GAIN_CH2 0b00111111 |

Definition at line 241 of file ADRF6650_Map.h.

◆ MASK_DVGA_GAIN_MODE

| #define MASK_DVGA_GAIN_MODE 0b00000111 |

Definition at line 230 of file ADRF6650_Map.h.

◆ MASK_DVGA_HP_SEL

| #define MASK_DVGA_HP_SEL 0b01000000 |

Definition at line 236 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_CH1_OVERRIDE_SEL

| #define MASK_DVGA_TRIM_CH1_OVERRIDE_SEL 0b00010000 |

Definition at line 287 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_CH2_OVERRIDE_SEL

| #define MASK_DVGA_TRIM_CH2_OVERRIDE_SEL 0b00100000 |

Definition at line 286 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_HP_3V_CH1_OVERRIDE

| #define MASK_DVGA_TRIM_HP_3V_CH1_OVERRIDE 0b00011111 |

Definition at line 263 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_HP_3V_CH2_OVERRIDE

| #define MASK_DVGA_TRIM_HP_3V_CH2_OVERRIDE 0b00011111 |

Definition at line 275 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_HP_5V_CH1_OVERRIDE

| #define MASK_DVGA_TRIM_HP_5V_CH1_OVERRIDE 0b00011111 |

Definition at line 269 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_HP_5V_CH2_OVERRIDE

| #define MASK_DVGA_TRIM_HP_5V_CH2_OVERRIDE 0b00011111 |

Definition at line 281 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_LP_3V_CH1_OVERRIDE

| #define MASK_DVGA_TRIM_LP_3V_CH1_OVERRIDE 0b00011111 |

Definition at line 260 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_LP_3V_CH2_OVERRIDE

| #define MASK_DVGA_TRIM_LP_3V_CH2_OVERRIDE 0b00011111 |

Definition at line 272 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_LP_5V_CH1_OVERRIDE

| #define MASK_DVGA_TRIM_LP_5V_CH1_OVERRIDE 0b00011111 |

Definition at line 266 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_LP_5V_CH2_OVERRIDE

| #define MASK_DVGA_TRIM_LP_5V_CH2_OVERRIDE 0b00011111 |

Definition at line 278 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_READBACK_CH1

| #define MASK_DVGA_TRIM_READBACK_CH1 0b11111111 |

Definition at line 180 of file ADRF6650_Map.h.

◆ MASK_DVGA_TRIM_READBACK_CH2

| #define MASK_DVGA_TRIM_READBACK_CH2 0b11111111 |

Definition at line 183 of file ADRF6650_Map.h.

◆ MASK_DVGA_UPDN_STEP

| #define MASK_DVGA_UPDN_STEP 0b00011000 |

Definition at line 229 of file ADRF6650_Map.h.

◆ MASK_EN_BIAS_R

| #define MASK_EN_BIAS_R 0b10000000 |

Definition at line 430 of file ADRF6650_Map.h.

◆ MASK_EN_FBDIV

| #define MASK_EN_FBDIV 0b00000001 |

Definition at line 360 of file ADRF6650_Map.h.

◆ MASK_EN_PFD_CP

| #define MASK_EN_PFD_CP 0b10000000 |

Definition at line 393 of file ADRF6650_Map.h.

◆ MASK_ENDIAN

| #define MASK_ENDIAN 0b00000100 |

Definition at line 120 of file ADRF6650_Map.h.

◆ MASK_ENDIAN_

| #define MASK_ENDIAN_ 0b00100000 |

Definition at line 117 of file ADRF6650_Map.h.

◆ MASK_FRAC15_8

| #define MASK_FRAC15_8 0b11111111 |

Definition at line 338 of file ADRF6650_Map.h.

◆ MASK_FRAC213_8

| #define MASK_FRAC213_8 0b00111111 |

Definition at line 411 of file ADRF6650_Map.h.

◆ MASK_FRAC23_16

| #define MASK_FRAC23_16 0b11111111 |

Definition at line 341 of file ADRF6650_Map.h.

◆ MASK_FRAC27_0

| #define MASK_FRAC27_0 0b11111111 |

Definition at line 408 of file ADRF6650_Map.h.

◆ MASK_FRAC2_SLV13_8

| #define MASK_FRAC2_SLV13_8 0b00111111 |

Definition at line 447 of file ADRF6650_Map.h.

◆ MASK_FRAC2_SLV7_0

| #define MASK_FRAC2_SLV7_0 0b11111111 |

Definition at line 444 of file ADRF6650_Map.h.

◆ MASK_FRAC7_0

| #define MASK_FRAC7_0 0b11111111 |

Definition at line 335 of file ADRF6650_Map.h.

◆ MASK_FRAC_SLV15_8

| #define MASK_FRAC_SLV15_8 0b11111111 |

Definition at line 453 of file ADRF6650_Map.h.

◆ MASK_FRAC_SLV23_16

| #define MASK_FRAC_SLV23_16 0b11111111 |

Definition at line 456 of file ADRF6650_Map.h.

◆ MASK_FRAC_SLV7_0

| #define MASK_FRAC_SLV7_0 0b11111111 |

Definition at line 450 of file ADRF6650_Map.h.

◆ MASK_GPO1_BLK_SEL

| #define MASK_GPO1_BLK_SEL 0b01111000 |

Definition at line 316 of file ADRF6650_Map.h.

◆ MASK_GPO1_ENABLE

| #define MASK_GPO1_ENABLE 0b00000001 |

Definition at line 317 of file ADRF6650_Map.h.

◆ MASK_GPO1_SGNL_SEL

| #define MASK_GPO1_SGNL_SEL 0b11111111 |

Definition at line 321 of file ADRF6650_Map.h.

◆ MASK_IF_ENB_CH1

| #define MASK_IF_ENB_CH1 0b00010000 |

Definition at line 189 of file ADRF6650_Map.h.

◆ MASK_IF_ENB_CH1_MASK

| #define MASK_IF_ENB_CH1_MASK 0b00001000 |

Definition at line 214 of file ADRF6650_Map.h.

◆ MASK_IF_ENB_CH2

| #define MASK_IF_ENB_CH2 0b00100000 |

Definition at line 188 of file ADRF6650_Map.h.

◆ MASK_IF_ENB_CH2_MASK

| #define MASK_IF_ENB_CH2_MASK 0b00010000 |

Definition at line 213 of file ADRF6650_Map.h.

◆ MASK_IFLIN_BIAS_EN

| #define MASK_IFLIN_BIAS_EN 0b00100000 |

Definition at line 203 of file ADRF6650_Map.h.

◆ MASK_IFLIN_BIAS_OVERRIDE

| #define MASK_IFLIN_BIAS_OVERRIDE 0b00001111 |

Definition at line 254 of file ADRF6650_Map.h.

◆ MASK_IFLIN_TRIM_OVERRIDE_SEL

| #define MASK_IFLIN_TRIM_OVERRIDE_SEL 0b00000100 |

Definition at line 289 of file ADRF6650_Map.h.

◆ MASK_IFMAIN_BIAS_EN

| #define MASK_IFMAIN_BIAS_EN 0b00010000 |

Definition at line 204 of file ADRF6650_Map.h.

◆ MASK_IFMAIN_BIAS_OVERRIDE

| #define MASK_IFMAIN_BIAS_OVERRIDE 0b00001111 |

Definition at line 251 of file ADRF6650_Map.h.

◆ MASK_IFMAIN_TRIM_OVERRIDE_SEL

| #define MASK_IFMAIN_TRIM_OVERRIDE_SEL 0b00000010 |

Definition at line 290 of file ADRF6650_Map.h.

◆ MASK_INT_ABP

| #define MASK_INT_ABP 0b00000100 |

Definition at line 395 of file ADRF6650_Map.h.

◆ MASK_INT_DIV15_8 [1/2]

| #define MASK_INT_DIV15_8 0b11111111 |

Definition at line 471 of file ADRF6650_Map.h.

◆ MASK_INT_DIV15_8 [2/2]

| #define MASK_INT_DIV15_8 0b11111111 |

Definition at line 471 of file ADRF6650_Map.h.

◆ MASK_INT_DIV7_0 [1/2]

| #define MASK_INT_DIV7_0 0b11111111 |

Definition at line 468 of file ADRF6650_Map.h.

◆ MASK_INT_DIV7_0 [2/2]

| #define MASK_INT_DIV7_0 0b11111111 |

Definition at line 468 of file ADRF6650_Map.h.

◆ MASK_LD_BIAS

| #define MASK_LD_BIAS 0b11000000 |

Definition at line 372 of file ADRF6650_Map.h.

◆ MASK_LDP

| #define MASK_LDP 0b00111000 |

Definition at line 373 of file ADRF6650_Map.h.

◆ MASK_LO_OE

| #define MASK_LO_OE 0b01000000 |

Definition at line 436 of file ADRF6650_Map.h.

◆ MASK_LO_STG1_ENB

| #define MASK_LO_STG1_ENB 0b00000010 |

Definition at line 192 of file ADRF6650_Map.h.

◆ MASK_LO_STG1_ENB_MASK

| #define MASK_LO_STG1_ENB_MASK 0b00000001 |

Definition at line 217 of file ADRF6650_Map.h.

◆ MASK_LO_STG23_ENB_CH1

| #define MASK_LO_STG23_ENB_CH1 0b00000100 |

Definition at line 191 of file ADRF6650_Map.h.

◆ MASK_LO_STG23_ENB_CH1_MASK

| #define MASK_LO_STG23_ENB_CH1_MASK 0b00000010 |

Definition at line 216 of file ADRF6650_Map.h.

◆ MASK_LO_STG23_ENB_CH2

| #define MASK_LO_STG23_ENB_CH2 0b00001000 |

Definition at line 190 of file ADRF6650_Map.h.

◆ MASK_LO_STG23_ENB_CH2_MASK

| #define MASK_LO_STG23_ENB_CH2_MASK 0b00000100 |

Definition at line 215 of file ADRF6650_Map.h.

◆ MASK_LOCK_DETECT

| #define MASK_LOCK_DETECT 0b00000001 |

Definition at line 424 of file ADRF6650_Map.h.

◆ MASK_LPF1_OVERRIDE

| #define MASK_LPF1_OVERRIDE 0b00001110 |

Definition at line 245 of file ADRF6650_Map.h.

◆ MASK_LPF2_OVERRIDE

| #define MASK_LPF2_OVERRIDE 0b01110000 |

Definition at line 244 of file ADRF6650_Map.h.

◆ MASK_LPF_DPLX_EN_OVERRIDE

| #define MASK_LPF_DPLX_EN_OVERRIDE 0b00000001 |

Definition at line 246 of file ADRF6650_Map.h.

◆ MASK_LPF_TRIM_OVERRIDE_SEL

| #define MASK_LPF_TRIM_OVERRIDE_SEL 0b00000001 |

Definition at line 291 of file ADRF6650_Map.h.

◆ MASK_LSB_FIRST

| #define MASK_LSB_FIRST 0b00000010 |

Definition at line 121 of file ADRF6650_Map.h.

◆ MASK_LSB_FIRST_

| #define MASK_LSB_FIRST_ 0b01000000 |

Definition at line 116 of file ADRF6650_Map.h.

◆ MASK_MASTER_SLAVE_RB

| #define MASK_MASTER_SLAVE_RB 0b00100000 |

Definition at line 134 of file ADRF6650_Map.h.

◆ MASK_MASTER_SLAVE_TRANSFER

| #define MASK_MASTER_SLAVE_TRANSFER 0b00000001 |

Definition at line 136 of file ADRF6650_Map.h.

◆ MASK_MIX_OE

| #define MASK_MIX_OE 0b10000000 |

Definition at line 435 of file ADRF6650_Map.h.

◆ MASK_MOD13_8

| #define MASK_MOD13_8 0b00111111 |

Definition at line 356 of file ADRF6650_Map.h.

◆ MASK_MOD7_0

| #define MASK_MOD7_0 0b11111111 |

Definition at line 353 of file ADRF6650_Map.h.

◆ MASK_OPERATING_MODE

| #define MASK_OPERATING_MODE 0b00001100 |

Definition at line 143 of file ADRF6650_Map.h.

◆ MASK_OUT_DIVRATIO

| #define MASK_OUT_DIVRATIO 0b00011111 |

Definition at line 438 of file ADRF6650_Map.h.

◆ MASK_PHASE15_8

| #define MASK_PHASE15_8 0b11111111 |

Definition at line 347 of file ADRF6650_Map.h.

◆ MASK_PHASE23_16

| #define MASK_PHASE23_16 0b11111111 |

Definition at line 350 of file ADRF6650_Map.h.

◆ MASK_PHASE7_0

| #define MASK_PHASE7_0 0b11111111 |

Definition at line 344 of file ADRF6650_Map.h.

◆ MASK_PHASE_ADJ_EN

| #define MASK_PHASE_ADJ_EN 0b00000010 |

Definition at line 414 of file ADRF6650_Map.h.

◆ MASK_PHASE_SLV15_8

| #define MASK_PHASE_SLV15_8 0b11111111 |

Definition at line 462 of file ADRF6650_Map.h.

◆ MASK_PHASE_SLV23_16

| #define MASK_PHASE_SLV23_16 0b11111111 |

Definition at line 465 of file ADRF6650_Map.h.

◆ MASK_PHASE_SLV7_0

| #define MASK_PHASE_SLV7_0 0b11111111 |

Definition at line 459 of file ADRF6650_Map.h.

◆ MASK_PLL_ENB_CH12_MASK

| #define MASK_PLL_ENB_CH12_MASK 0b10000000 |

Definition at line 210 of file ADRF6650_Map.h.

◆ MASK_POWER_MODE

| #define MASK_POWER_MODE 0b00000011 |

Definition at line 144 of file ADRF6650_Map.h.

◆ MASK_PRE_SEL

| #define MASK_PRE_SEL 0b00000010 |

Definition at line 359 of file ADRF6650_Map.h.

◆ MASK_PRODUCT_ID_1

| #define MASK_PRODUCT_ID_1 0b11111111 |

Definition at line 151 of file ADRF6650_Map.h.

◆ MASK_PRODUCT_ID_2

| #define MASK_PRODUCT_ID_2 0b11111111 |

Definition at line 154 of file ADRF6650_Map.h.

◆ MASK_R_DIV

| #define MASK_R_DIV 0b01111111 |

Definition at line 364 of file ADRF6650_Map.h.

◆ MASK_R_DIV_SLV

| #define MASK_R_DIV_SLV 0b01111111 |

Definition at line 474 of file ADRF6650_Map.h.

◆ MASK_RDIV2_SEL

| #define MASK_RDIV2_SEL 0b00000001 |

Definition at line 368 of file ADRF6650_Map.h.

◆ MASK_RDIV2_SEL_SLV

| #define MASK_RDIV2_SEL_SLV 0b00000001 |

Definition at line 477 of file ADRF6650_Map.h.

◆ MASK_REFBUF_EN

| #define MASK_REFBUF_EN 0b00100000 |

Definition at line 431 of file ADRF6650_Map.h.

◆ MASK_SCRATCHPAD

| #define MASK_SCRATCHPAD 0b11111111 |

Definition at line 157 of file ADRF6650_Map.h.

◆ MASK_SD_EN_FRAC0

| #define MASK_SD_EN_FRAC0 0b00100000 |

Definition at line 383 of file ADRF6650_Map.h.

◆ MASK_SD_EN_OUT_OFF

| #define MASK_SD_EN_OUT_OFF 0b00010000 |

Definition at line 384 of file ADRF6650_Map.h.

◆ MASK_SD_SM_2

| #define MASK_SD_SM_2 0b00000010 |

Definition at line 385 of file ADRF6650_Map.h.

◆ MASK_SDOACTIVE

| #define MASK_SDOACTIVE 0b00001000 |

Definition at line 119 of file ADRF6650_Map.h.

◆ MASK_SDOACTIVE_

| #define MASK_SDOACTIVE_ 0b00010000 |

Definition at line 118 of file ADRF6650_Map.h.

◆ MASK_SI_VCO_FORCE_CAPS

| #define MASK_SI_VCO_FORCE_CAPS 0b00000001 |

Definition at line 419 of file ADRF6650_Map.h.

◆ MASK_SI_VCO_FORCE_CAPSVCOI

| #define MASK_SI_VCO_FORCE_CAPSVCOI 0b00010000 |

Definition at line 417 of file ADRF6650_Map.h.

◆ MASK_SI_VCO_FORCE_VCO

| #define MASK_SI_VCO_FORCE_VCO 0b00000010 |

Definition at line 418 of file ADRF6650_Map.h.

◆ MASK_SI_VCO_SEL

| #define MASK_SI_VCO_SEL 0b00001111 |

Definition at line 377 of file ADRF6650_Map.h.

◆ MASK_SINGLE_INSTRUCTION

| #define MASK_SINGLE_INSTRUCTION 0b10000000 |

Definition at line 132 of file ADRF6650_Map.h.

◆ MASK_SOFTRESET

| #define MASK_SOFTRESET 0b00000001 |

Definition at line 122 of file ADRF6650_Map.h.

◆ MASK_SOFTRESET_

| #define MASK_SOFTRESET_ 0b10000000 |

Definition at line 115 of file ADRF6650_Map.h.

◆ MASK_SOFTRESET_B

| #define MASK_SOFTRESET_B 0b00000110 |

Definition at line 135 of file ADRF6650_Map.h.

◆ MASK_SPARE1_OVERRIDE_SEL

| #define MASK_SPARE1_OVERRIDE_SEL 0b01000000 |

Definition at line 285 of file ADRF6650_Map.h.

◆ MASK_SPARE2_OVERRIDE_SEL

| #define MASK_SPARE2_OVERRIDE_SEL 0b10000000 |

Definition at line 284 of file ADRF6650_Map.h.

◆ MASK_SPI_18_33_SEL

| #define MASK_SPI_18_33_SEL 0b00000001 |

Definition at line 205 of file ADRF6650_Map.h.

◆ MASK_SPI_1P8_3P3_CTRL

| #define MASK_SPI_1P8_3P3_CTRL 0b00010000 |

Definition at line 427 of file ADRF6650_Map.h.

◆ MASK_SPI_VER

| #define MASK_SPI_VER 0b11111111 |

Definition at line 160 of file ADRF6650_Map.h.

◆ MASK_TRM_MIXLODRV_DRV_POUT

| #define MASK_TRM_MIXLODRV_DRV_POUT 0b00011000 |

Definition at line 324 of file ADRF6650_Map.h.

◆ MASK_TRM_XLODRV_DRV_POUT

| #define MASK_TRM_XLODRV_DRV_POUT 0b00000110 |

Definition at line 325 of file ADRF6650_Map.h.

◆ MASK_USEEXT_LOI

| #define MASK_USEEXT_LOI 0b00100000 |

Definition at line 437 of file ADRF6650_Map.h.

◆ MASK_VENDOR_ID15_8

| #define MASK_VENDOR_ID15_8 0b11111111 |

Definition at line 166 of file ADRF6650_Map.h.

◆ MASK_VENDOR_ID7_0

| #define MASK_VENDOR_ID7_0 0b11111111 |

Definition at line 163 of file ADRF6650_Map.h.

◆ MASK_VGS_OVERRIDE

| #define MASK_VGS_OVERRIDE 0b00001111 |

Definition at line 257 of file ADRF6650_Map.h.

◆ MASK_VGS_OVERRIDE_SEL

| #define MASK_VGS_OVERRIDE_SEL 0b00001000 |

Definition at line 288 of file ADRF6650_Map.h.

◆ SHIFT__GPO1_BLK_SEL

| #define SHIFT__GPO1_BLK_SEL 3 |

Definition at line 318 of file ADRF6650_Map.h.

◆ SHIFT__GPO1_ENABLE

| #define SHIFT__GPO1_ENABLE 0 |

Definition at line 319 of file ADRF6650_Map.h.

◆ SHIFT_ARSTB_BLOCK_AUTOCAL

| #define SHIFT_ARSTB_BLOCK_AUTOCAL 5 |

Definition at line 309 of file ADRF6650_Map.h.

◆ SHIFT_ARSTB_BLOCK_DSMALL

| #define SHIFT_ARSTB_BLOCK_DSMALL 0 |

Definition at line 314 of file ADRF6650_Map.h.

◆ SHIFT_ARSTB_BLOCK_DSMCORE

| #define SHIFT_ARSTB_BLOCK_DSMCORE 1 |

Definition at line 313 of file ADRF6650_Map.h.

◆ SHIFT_ARSTB_BLOCK_DSMOSTG

| #define SHIFT_ARSTB_BLOCK_DSMOSTG 2 |

Definition at line 312 of file ADRF6650_Map.h.

◆ SHIFT_ARSTB_BLOCK_LKD

| #define SHIFT_ARSTB_BLOCK_LKD 6 |

Definition at line 308 of file ADRF6650_Map.h.

◆ SHIFT_ARSTB_BLOCK_NDIV

| #define SHIFT_ARSTB_BLOCK_NDIV 4 |

Definition at line 310 of file ADRF6650_Map.h.

◆ SHIFT_ARSTB_BLOCK_RDIV

| #define SHIFT_ARSTB_BLOCK_RDIV 3 |

Definition at line 311 of file ADRF6650_Map.h.

◆ SHIFT_ATTEN_READBACK_CH1

| #define SHIFT_ATTEN_READBACK_CH1 0 |

Definition at line 175 of file ADRF6650_Map.h.

◆ SHIFT_ATTEN_READBACK_CH2

| #define SHIFT_ATTEN_READBACK_CH2 0 |

Definition at line 178 of file ADRF6650_Map.h.

◆ SHIFT_BICP

| #define SHIFT_BICP 0 |

Definition at line 406 of file ADRF6650_Map.h.

◆ SHIFT_BLEED_EN_

| #define SHIFT_BLEED_EN_ 0 |

Definition at line 400 of file ADRF6650_Map.h.

◆ SHIFT_BLEED_POL

| #define SHIFT_BLEED_POL 6 |

Definition at line 398 of file ADRF6650_Map.h.

◆ SHIFT_BYPASS_TDD

| #define SHIFT_BYPASS_TDD 0 |

Definition at line 201 of file ADRF6650_Map.h.

◆ SHIFT_CHIPTYPE

| #define SHIFT_CHIPTYPE 0 |

Definition at line 149 of file ADRF6650_Map.h.

◆ SHIFT_CP_CURRENT

| #define SHIFT_CP_CURRENT 0 |

Definition at line 403 of file ADRF6650_Map.h.

◆ SHIFT_CP_HIZ

| #define SHIFT_CP_HIZ 0 |

Definition at line 391 of file ADRF6650_Map.h.

◆ SHIFT_CSB_STALL

| #define SHIFT_CSB_STALL 6 |

Definition at line 138 of file ADRF6650_Map.h.

◆ SHIFT_DISABLE_CAL

| #define SHIFT_DISABLE_CAL 6 |

Definition at line 381 of file ADRF6650_Map.h.

◆ SHIFT_DISABLE_DBLBUFFERING

| #define SHIFT_DISABLE_DBLBUFFERING 1 |

Definition at line 486 of file ADRF6650_Map.h.

◆ SHIFT_DISABLE_FREQHOP

| #define SHIFT_DISABLE_FREQHOP 2 |

Definition at line 485 of file ADRF6650_Map.h.

◆ SHIFT_DISABLE_PHASEADJ

| #define SHIFT_DISABLE_PHASEADJ 0 |

Definition at line 487 of file ADRF6650_Map.h.

◆ SHIFT_DOUBLER_EN

| #define SHIFT_DOUBLER_EN 3 |

Definition at line 369 of file ADRF6650_Map.h.

◆ SHIFT_DSM_LAUNCH_DLY

| #define SHIFT_DSM_LAUNCH_DLY 3 |

Definition at line 484 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_5V_SEL

| #define SHIFT_DVGA_5V_SEL 7 |

Definition at line 231 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_CH1_RSTB

| #define SHIFT_DVGA_CH1_RSTB 0 |

Definition at line 172 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_CH2_RSTB

| #define SHIFT_DVGA_CH2_RSTB 1 |

Definition at line 171 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_ENB_CH1

| #define SHIFT_DVGA_ENB_CH1 6 |

Definition at line 195 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_ENB_CH1_MASK

| #define SHIFT_DVGA_ENB_CH1_MASK 5 |

Definition at line 220 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_ENB_CH2

| #define SHIFT_DVGA_ENB_CH2 7 |

Definition at line 194 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_ENB_CH2_MASK

| #define SHIFT_DVGA_ENB_CH2_MASK 6 |

Definition at line 219 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_FA_STEP

| #define SHIFT_DVGA_FA_STEP 5 |

Definition at line 232 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_GAIN_CH1

| #define SHIFT_DVGA_GAIN_CH1 0 |

Definition at line 239 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_GAIN_CH2

| #define SHIFT_DVGA_GAIN_CH2 0 |

Definition at line 242 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_GAIN_MODE

| #define SHIFT_DVGA_GAIN_MODE 0 |

Definition at line 234 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_HP_SEL

| #define SHIFT_DVGA_HP_SEL 6 |

Definition at line 238 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_TRIM_CH1_OVERRIDE_SEL

| #define SHIFT_DVGA_TRIM_CH1_OVERRIDE_SEL 4 |

Definition at line 295 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_TRIM_CH2_OVERRIDE_SEL

| #define SHIFT_DVGA_TRIM_CH2_OVERRIDE_SEL 5 |

Definition at line 294 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_TRIM_READBACK_CH1

| #define SHIFT_DVGA_TRIM_READBACK_CH1 0 |

Definition at line 181 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_TRIM_READBACK_CH2

| #define SHIFT_DVGA_TRIM_READBACK_CH2 0 |

Definition at line 184 of file ADRF6650_Map.h.

◆ SHIFT_DVGA_UPDN_STEP

| #define SHIFT_DVGA_UPDN_STEP 3 |

Definition at line 233 of file ADRF6650_Map.h.

◆ SHIFT_EN_BIAS_R

| #define SHIFT_EN_BIAS_R 7 |

Definition at line 432 of file ADRF6650_Map.h.

◆ SHIFT_EN_FBDIV

| #define SHIFT_EN_FBDIV 0 |

Definition at line 362 of file ADRF6650_Map.h.

◆ SHIFT_EN_PFD_CP

| #define SHIFT_EN_PFD_CP 7 |

Definition at line 397 of file ADRF6650_Map.h.

◆ SHIFT_ENDIAN

| #define SHIFT_ENDIAN 2 |

Definition at line 128 of file ADRF6650_Map.h.

◆ SHIFT_ENDIAN_

| #define SHIFT_ENDIAN_ 5 |

Definition at line 125 of file ADRF6650_Map.h.

◆ SHIFT_FRAC15_8

| #define SHIFT_FRAC15_8 0 |

Definition at line 339 of file ADRF6650_Map.h.

◆ SHIFT_FRAC213_8

| #define SHIFT_FRAC213_8 0 |

Definition at line 412 of file ADRF6650_Map.h.

◆ SHIFT_FRAC23_16

| #define SHIFT_FRAC23_16 0 |

Definition at line 342 of file ADRF6650_Map.h.

◆ SHIFT_FRAC27_0

| #define SHIFT_FRAC27_0 0 |

Definition at line 409 of file ADRF6650_Map.h.

◆ SHIFT_FRAC2_SLV13_8

| #define SHIFT_FRAC2_SLV13_8 0 |

Definition at line 448 of file ADRF6650_Map.h.

◆ SHIFT_FRAC2_SLV7_0

| #define SHIFT_FRAC2_SLV7_0 0 |

Definition at line 445 of file ADRF6650_Map.h.

◆ SHIFT_FRAC7_0

| #define SHIFT_FRAC7_0 0 |

Definition at line 336 of file ADRF6650_Map.h.

◆ SHIFT_FRAC_SLV15_8

| #define SHIFT_FRAC_SLV15_8 0 |

Definition at line 454 of file ADRF6650_Map.h.

◆ SHIFT_FRAC_SLV23_16

| #define SHIFT_FRAC_SLV23_16 0 |

Definition at line 457 of file ADRF6650_Map.h.

◆ SHIFT_FRAC_SLV7_0

| #define SHIFT_FRAC_SLV7_0 0 |

Definition at line 451 of file ADRF6650_Map.h.

◆ SHIFT_GPO1_SGNL_SEL

| #define SHIFT_GPO1_SGNL_SEL 0 |

Definition at line 322 of file ADRF6650_Map.h.

◆ SHIFT_IF_ENB_CH1

| #define SHIFT_IF_ENB_CH1 4 |

Definition at line 197 of file ADRF6650_Map.h.

◆ SHIFT_IF_ENB_CH1_MASK

| #define SHIFT_IF_ENB_CH1_MASK 3 |

Definition at line 222 of file ADRF6650_Map.h.

◆ SHIFT_IF_ENB_CH2

| #define SHIFT_IF_ENB_CH2 5 |

Definition at line 196 of file ADRF6650_Map.h.

◆ SHIFT_IF_ENB_CH2_MASK

| #define SHIFT_IF_ENB_CH2_MASK 4 |

Definition at line 221 of file ADRF6650_Map.h.

◆ SHIFT_IFLIN_BIAS_EN

| #define SHIFT_IFLIN_BIAS_EN 5 |

Definition at line 206 of file ADRF6650_Map.h.

◆ SHIFT_IFLIN_BIAS_OVERRIDE

| #define SHIFT_IFLIN_BIAS_OVERRIDE 0 |

Definition at line 255 of file ADRF6650_Map.h.

◆ SHIFT_IFLIN_TRIM_OVERRIDE_SEL

| #define SHIFT_IFLIN_TRIM_OVERRIDE_SEL 2 |

Definition at line 297 of file ADRF6650_Map.h.

◆ SHIFT_IFMAIN_BIAS_EN

| #define SHIFT_IFMAIN_BIAS_EN 4 |

Definition at line 207 of file ADRF6650_Map.h.

◆ SHIFT_IFMAIN_BIAS_OVERRIDE

| #define SHIFT_IFMAIN_BIAS_OVERRIDE 0 |

Definition at line 252 of file ADRF6650_Map.h.

◆ SHIFT_IFMAIN_TRIM_OVERRIDE_SEL

| #define SHIFT_IFMAIN_TRIM_OVERRIDE_SEL 1 |

Definition at line 298 of file ADRF6650_Map.h.

◆ SHIFT_INT_ABP

| #define SHIFT_INT_ABP 2 |

Definition at line 399 of file ADRF6650_Map.h.

◆ SHIFT_INT_DIV15_8 [1/2]

| #define SHIFT_INT_DIV15_8 0 |

Definition at line 472 of file ADRF6650_Map.h.

◆ SHIFT_INT_DIV15_8 [2/2]

| #define SHIFT_INT_DIV15_8 0 |

Definition at line 472 of file ADRF6650_Map.h.

◆ SHIFT_INT_DIV7_0 [1/2]

| #define SHIFT_INT_DIV7_0 0 |

Definition at line 469 of file ADRF6650_Map.h.

◆ SHIFT_INT_DIV7_0 [2/2]

| #define SHIFT_INT_DIV7_0 0 |

Definition at line 469 of file ADRF6650_Map.h.

◆ SHIFT_LD_BIAS

| #define SHIFT_LD_BIAS 6 |

Definition at line 374 of file ADRF6650_Map.h.

◆ SHIFT_LDP

| #define SHIFT_LDP 3 |

Definition at line 375 of file ADRF6650_Map.h.

◆ SHIFT_LO_OE

| #define SHIFT_LO_OE 6 |

Definition at line 440 of file ADRF6650_Map.h.

◆ SHIFT_LO_STG1_ENB

| #define SHIFT_LO_STG1_ENB 1 |

Definition at line 200 of file ADRF6650_Map.h.

◆ SHIFT_LO_STG1_ENB_MASK

| #define SHIFT_LO_STG1_ENB_MASK 0 |

Definition at line 225 of file ADRF6650_Map.h.

◆ SHIFT_LO_STG23_ENB_CH1

| #define SHIFT_LO_STG23_ENB_CH1 2 |

Definition at line 199 of file ADRF6650_Map.h.

◆ SHIFT_LO_STG23_ENB_CH1_MASK

| #define SHIFT_LO_STG23_ENB_CH1_MASK 1 |

Definition at line 224 of file ADRF6650_Map.h.

◆ SHIFT_LO_STG23_ENB_CH2

| #define SHIFT_LO_STG23_ENB_CH2 3 |

Definition at line 198 of file ADRF6650_Map.h.

◆ SHIFT_LO_STG23_ENB_CH2_MASK

| #define SHIFT_LO_STG23_ENB_CH2_MASK 2 |

Definition at line 223 of file ADRF6650_Map.h.

◆ SHIFT_LOCK_DETECT

| #define SHIFT_LOCK_DETECT 0 |

Definition at line 425 of file ADRF6650_Map.h.

◆ SHIFT_LPF1_OVERRIDE

| #define SHIFT_LPF1_OVERRIDE 1 |

Definition at line 248 of file ADRF6650_Map.h.

◆ SHIFT_LPF2_OVERRIDE

| #define SHIFT_LPF2_OVERRIDE 4 |

Definition at line 247 of file ADRF6650_Map.h.

◆ SHIFT_LPF_DPLX_EN_OVERRIDE

| #define SHIFT_LPF_DPLX_EN_OVERRIDE 0 |

Definition at line 249 of file ADRF6650_Map.h.

◆ SHIFT_LPF_TRIM_OVERRIDE_SEL

| #define SHIFT_LPF_TRIM_OVERRIDE_SEL 0 |

Definition at line 299 of file ADRF6650_Map.h.

◆ SHIFT_LSB_FIRST

| #define SHIFT_LSB_FIRST 1 |

Definition at line 129 of file ADRF6650_Map.h.

◆ SHIFT_LSB_FIRST_

| #define SHIFT_LSB_FIRST_ 6 |

Definition at line 124 of file ADRF6650_Map.h.

◆ SHIFT_MASTER_SLAVE_RB

| #define SHIFT_MASTER_SLAVE_RB 5 |

Definition at line 139 of file ADRF6650_Map.h.

◆ SHIFT_MASTER_SLAVE_TRANSFER

| #define SHIFT_MASTER_SLAVE_TRANSFER 0 |

Definition at line 141 of file ADRF6650_Map.h.

◆ SHIFT_MIX_OE

| #define SHIFT_MIX_OE 7 |

Definition at line 439 of file ADRF6650_Map.h.

◆ SHIFT_MOD13_8

| #define SHIFT_MOD13_8 0 |

Definition at line 357 of file ADRF6650_Map.h.

◆ SHIFT_MOD7_0

| #define SHIFT_MOD7_0 0 |

Definition at line 354 of file ADRF6650_Map.h.

◆ SHIFT_OPERATING_MODE

| #define SHIFT_OPERATING_MODE 2 |

Definition at line 145 of file ADRF6650_Map.h.

◆ SHIFT_OUT_DIVRATIO

| #define SHIFT_OUT_DIVRATIO 0 |

Definition at line 442 of file ADRF6650_Map.h.

◆ SHIFT_PHASE15_8

| #define SHIFT_PHASE15_8 0 |

Definition at line 348 of file ADRF6650_Map.h.

◆ SHIFT_PHASE23_16

| #define SHIFT_PHASE23_16 0 |

Definition at line 351 of file ADRF6650_Map.h.

◆ SHIFT_PHASE7_0

| #define SHIFT_PHASE7_0 0 |

Definition at line 345 of file ADRF6650_Map.h.

◆ SHIFT_PHASE_ADJ_EN

| #define SHIFT_PHASE_ADJ_EN 1 |

Definition at line 415 of file ADRF6650_Map.h.

◆ SHIFT_PHASE_SLV15_8

| #define SHIFT_PHASE_SLV15_8 0 |

Definition at line 463 of file ADRF6650_Map.h.

◆ SHIFT_PHASE_SLV23_16

| #define SHIFT_PHASE_SLV23_16 0 |

Definition at line 466 of file ADRF6650_Map.h.

◆ SHIFT_PHASE_SLV7_0

| #define SHIFT_PHASE_SLV7_0 0 |

Definition at line 460 of file ADRF6650_Map.h.

◆ SHIFT_PLL_ENB_CH12_MASK

| #define SHIFT_PLL_ENB_CH12_MASK 7 |

Definition at line 218 of file ADRF6650_Map.h.

◆ SHIFT_POWER_MODE

| #define SHIFT_POWER_MODE 0 |

Definition at line 146 of file ADRF6650_Map.h.

◆ SHIFT_PRE_SEL

| #define SHIFT_PRE_SEL 1 |

Definition at line 361 of file ADRF6650_Map.h.

◆ SHIFT_PRODUCT_ID_1

| #define SHIFT_PRODUCT_ID_1 0 |

Definition at line 152 of file ADRF6650_Map.h.

◆ SHIFT_PRODUCT_ID_2

| #define SHIFT_PRODUCT_ID_2 0 |

Definition at line 155 of file ADRF6650_Map.h.

◆ SHIFT_R_DIV

| #define SHIFT_R_DIV 0 |

Definition at line 365 of file ADRF6650_Map.h.

◆ SHIFT_R_DIV_SLV

| #define SHIFT_R_DIV_SLV 0 |

Definition at line 475 of file ADRF6650_Map.h.

◆ SHIFT_RDIV2_SEL

| #define SHIFT_RDIV2_SEL 0 |

Definition at line 370 of file ADRF6650_Map.h.

◆ SHIFT_RDIV2_SEL_SLV

| #define SHIFT_RDIV2_SEL_SLV 0 |

Definition at line 478 of file ADRF6650_Map.h.

◆ SHIFT_REFBUF_EN

| #define SHIFT_REFBUF_EN 5 |

Definition at line 433 of file ADRF6650_Map.h.

◆ SHIFT_SCRATCHPAD

| #define SHIFT_SCRATCHPAD 0 |

Definition at line 158 of file ADRF6650_Map.h.

◆ SHIFT_SD_EN_FRAC0

| #define SHIFT_SD_EN_FRAC0 5 |

Definition at line 386 of file ADRF6650_Map.h.

◆ SHIFT_SD_EN_OUT_OFF

| #define SHIFT_SD_EN_OUT_OFF 4 |

Definition at line 387 of file ADRF6650_Map.h.

◆ SHIFT_SD_SM_2

| #define SHIFT_SD_SM_2 0 |

Definition at line 388 of file ADRF6650_Map.h.

◆ SHIFT_SDOACTIVE

| #define SHIFT_SDOACTIVE 3 |

Definition at line 127 of file ADRF6650_Map.h.

◆ SHIFT_SDOACTIVE_

| #define SHIFT_SDOACTIVE_ 4 |

Definition at line 126 of file ADRF6650_Map.h.

◆ SHIFT_SI_VCO_FORCE_CAPS

| #define SHIFT_SI_VCO_FORCE_CAPS 0 |

Definition at line 422 of file ADRF6650_Map.h.

◆ SHIFT_SI_VCO_FORCE_CAPSVCOI

| #define SHIFT_SI_VCO_FORCE_CAPSVCOI 4 |

Definition at line 420 of file ADRF6650_Map.h.

◆ SHIFT_SI_VCO_FORCE_VCO

| #define SHIFT_SI_VCO_FORCE_VCO 1 |

Definition at line 421 of file ADRF6650_Map.h.

◆ SHIFT_SI_VCO_SEL

| #define SHIFT_SI_VCO_SEL 0 |

Definition at line 378 of file ADRF6650_Map.h.

◆ SHIFT_SINGLE_INSTRUCTION

| #define SHIFT_SINGLE_INSTRUCTION 7 |

Definition at line 137 of file ADRF6650_Map.h.

◆ SHIFT_SOFTRESET

| #define SHIFT_SOFTRESET 0 |

Definition at line 130 of file ADRF6650_Map.h.

◆ SHIFT_SOFTRESET_

| #define SHIFT_SOFTRESET_ 7 |

Definition at line 123 of file ADRF6650_Map.h.

◆ SHIFT_SOFTRESET_B

| #define SHIFT_SOFTRESET_B 1 |

Definition at line 140 of file ADRF6650_Map.h.

◆ SHIFT_SPARE1_OVERRIDE_SEL

| #define SHIFT_SPARE1_OVERRIDE_SEL 6 |

Definition at line 293 of file ADRF6650_Map.h.

◆ SHIFT_SPARE2_OVERRIDE_SEL

| #define SHIFT_SPARE2_OVERRIDE_SEL 7 |

Definition at line 292 of file ADRF6650_Map.h.

◆ SHIFT_SPI_18_33_SEL

| #define SHIFT_SPI_18_33_SEL 0 |

Definition at line 208 of file ADRF6650_Map.h.

◆ SHIFT_SPI_1P8_3P3_CTRL

| #define SHIFT_SPI_1P8_3P3_CTRL 4 |

Definition at line 428 of file ADRF6650_Map.h.

◆ SHIFT_SPI_VER

| #define SHIFT_SPI_VER 0 |

Definition at line 161 of file ADRF6650_Map.h.

◆ SHIFT_TRM_MIXLODRV_DRV_POUT

| #define SHIFT_TRM_MIXLODRV_DRV_POUT 3 |

Definition at line 326 of file ADRF6650_Map.h.

◆ SHIFT_TRM_XLODRV_DRV_POUT

| #define SHIFT_TRM_XLODRV_DRV_POUT 1 |

Definition at line 327 of file ADRF6650_Map.h.

◆ SHIFT_USEEXT_LOI

| #define SHIFT_USEEXT_LOI 5 |

Definition at line 441 of file ADRF6650_Map.h.

◆ SHIFT_VENDOR_ID15_8

| #define SHIFT_VENDOR_ID15_8 0 |

Definition at line 167 of file ADRF6650_Map.h.

◆ SHIFT_VENDOR_ID7_0

| #define SHIFT_VENDOR_ID7_0 0 |

Definition at line 164 of file ADRF6650_Map.h.

◆ SHIFT_VGS_OVERRIDE

| #define SHIFT_VGS_OVERRIDE 0 |

Definition at line 258 of file ADRF6650_Map.h.

◆ SHIFT_VGS_OVERRIDE_SEL

| #define SHIFT_VGS_OVERRIDE_SEL 3 |

Definition at line 296 of file ADRF6650_Map.h.

◆ SHIFTDVGA_TRIM_HP_3V_CH1_OVERRIDE

| #define SHIFTDVGA_TRIM_HP_3V_CH1_OVERRIDE 0 |

Definition at line 264 of file ADRF6650_Map.h.

◆ SHIFTDVGA_TRIM_HP_3V_CH2_OVERRIDE

| #define SHIFTDVGA_TRIM_HP_3V_CH2_OVERRIDE 0 |

Definition at line 276 of file ADRF6650_Map.h.

◆ SHIFTDVGA_TRIM_HP_5V_CH1_OVERRIDE

| #define SHIFTDVGA_TRIM_HP_5V_CH1_OVERRIDE 0 |

Definition at line 270 of file ADRF6650_Map.h.

◆ SHIFTDVGA_TRIM_HP_5V_CH2_OVERRIDE

| #define SHIFTDVGA_TRIM_HP_5V_CH2_OVERRIDE 0 |

Definition at line 282 of file ADRF6650_Map.h.

◆ SHIFTDVGA_TRIM_LP_3V_CH1_OVERRIDE

| #define SHIFTDVGA_TRIM_LP_3V_CH1_OVERRIDE 0 |

Definition at line 261 of file ADRF6650_Map.h.

◆ SHIFTDVGA_TRIM_LP_3V_CH2_OVERRIDE

| #define SHIFTDVGA_TRIM_LP_3V_CH2_OVERRIDE 0 |

Definition at line 273 of file ADRF6650_Map.h.

◆ SHIFTDVGA_TRIM_LP_5V_CH1_OVERRIDE

| #define SHIFTDVGA_TRIM_LP_5V_CH1_OVERRIDE 0 |

Definition at line 267 of file ADRF6650_Map.h.

◆ SHIFTDVGA_TRIM_LP_5V_CH2_OVERRIDE

| #define SHIFTDVGA_TRIM_LP_5V_CH2_OVERRIDE 0 |

Definition at line 279 of file ADRF6650_Map.h.

Enumeration Type Documentation

◆ register_addr_t

| enum register_addr_t |

Definition at line 30 of file ADRF6650_Map.h.